(报告出品方/作者:民生证券,方竞、张文雨)

1 先进封装引领摩尔定律延续

半导体封装是半导体制造工艺的后道工序,是指将通过测试的晶圆加工得到 独立芯片的过程,即将制作好的半导体器件放入具有支持、保护的塑料、陶瓷或 金属外壳中,并与外界驱动电路及其他电子元器件相连的过程。

1.1 先进封装发展历程

迄今为止全球集成电路封装技术一共经历了五个发展阶段。通常认为,前三 个阶段属于传统封装,第四、五阶段属于先进封装。当前的主流技术处于以 CSP、 BGA 为主的第三阶段,且正在从传统封装(SOT、QFN、BGA 等)向先进封装 (FC、FIWLP、FOWLP、TSV、SIP 等)转型。

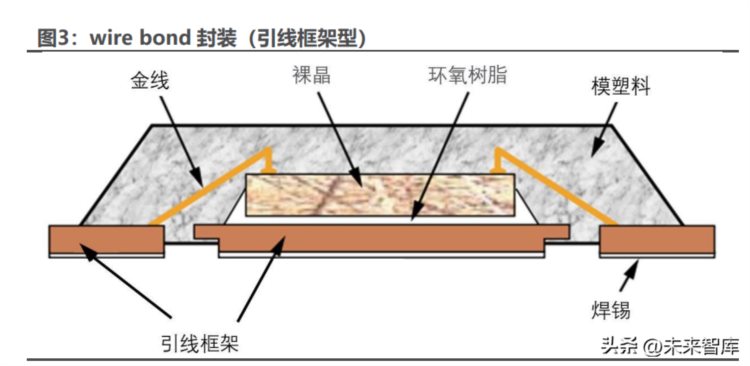

传统封装以引线框架型封装为主,芯片与引线框架通过焊线连接,引线框架 的接脚连接 PCB,主要包括 DIP、SOP、QFP、QFN 等封装形式。

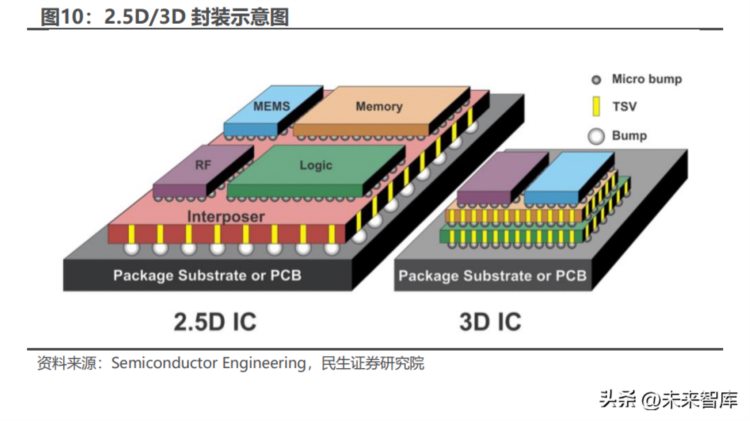

传统封装的功能主要在于芯片保护、尺度放大、电气连接三项功能,先进封 装技术则对芯片进行封装级重构,能有效提高系统高功能密度。现阶段先进封装 主要是指倒装焊(Flip Chip)、晶圆级封装(WLP)、2.5D 封装(Interposer)和 3D 封装(TSV)等。 先进封装与传统封装的主要区别在于一级互联和二级互联方式的不同。 一级互联方式主要包括:传统工艺—Wire Bonding(WB);先进工艺— Flip Chip(FC)。 二级互联方式主要包括:传统工艺—通孔插装型/表面贴装;先进工艺—球栅阵列型(BGA)/平面网格阵列 LGA/插针网格阵列(PGA)。 因此 FCBGA、FCLGA 等封装就称为先进封装。同时,传统的元件封装也演 变为系统封装,封装对象由单芯片向多芯片发展,由平面封装向立体封装发展。

市场规模方面,据 Yole 和集微咨询数据,2017 年以来全球封测市场规模稳 健增长,2022 年达到 815 亿美元。Yole 预计总体市场规模将保持增长态势, 2026 年达到 961 亿美元。

先进封装则有望展现高于封测市场整体的增长水平。据 Yole 预计,2019- 2025 年,全球整体封装市场规模年均复合增速 4%,先进封装市场规模则达到 7% 的年均复合增速,并在 2025 年占据整体封装市场的 49.4%。

1.2 先进封装助力摩尔定律延续

摩尔定律主要内容为:在价格不变时,集成电路上可以容纳的晶体管数量每 18-24 个月便会增加一倍,即:处理器性能大约每两年翻一倍,同时价格下降为 之前的一半。 自 2015 年以来,集成电路先进制程的发展开始放缓,7nm、5nm、3nm 制 程的量产进度均落后于预期。随着台积电宣布 2nm 制程工艺实现突破,集成电 路制程工艺已接近物理尺寸极限;与此同时芯片设计成本快速提升,以先进工艺 节点处于主流应用时期设计成本为例,工艺节点为 28nm 时,单颗芯片设计成本 约为 0.41 亿美元,而工艺节点为 7nm 时设计成本提升至 2.22 亿美元。

为有效降低成本、进一步提升芯片性能、丰富芯片功能,各家龙头厂商争相 探索先进封装技术。先进封装技术作为提高连接密度、提高系统集成度与小型化 的重要方法,在单芯片向更高端制程推进难度大增时,担负起延续摩尔定律的重 任。

如今,除了单个芯片封装形式的演进以外,多芯片集成、2.5D/3D 堆叠等技 术也成为现阶段先进封装的主流技术路径,尤其对于大规模集成电路,Chiplet 封装技术应运而生发挥重要作用,我们将在下文重点讨论。

2 Chiplet:算力时代的共同选择

2.1 算力时代来临,算力芯片降本增效需求凸显

AI技术蓬勃发展的当下,数据中心对高算力芯片的需求急速增长。GPU 由于 具备并行计算能力,可兼容训练和推理,高度适配 AI 模型构建,目前被广泛应用 于加速芯片。随着 ChatGPT 带来新的 AI 应用热潮,数据中心对高算力的 GPU 芯 片需求急速增长。 相较于传统消费级芯片,算力芯片面积更大,存储容量更大,对互连速度要 求更高,而 Chiplet 技术可以很好的满足这些大规模芯片的性能和成本需求,因 而得到广泛运用。

Chiplet 即小芯粒,它将一类满足特定功能的 die(裸片),通过 die-to-die 内部互联技术将多个模块芯片与底层基础芯片封装在一起,形成一个系统芯片。

2.2 Chiplet 技术在算力芯片领域的三大优势

(1)大面积芯片降低成本提升良率

由于更高的性能需求,算力芯片的 die size 通常要远大于过去的消费级产品。 例如 Nvdia 主流 AI 加速卡产品,die size 通常超过 800mm2。而近年来,随着 先进制程推进,研发生产成本持续走高,大面积单颗 SOC 良率日益下降。 Chiplet 将单颗 SOC 的不同功能模块拆分成独立的小芯粒(即 Chiplet), 大大缩小了单颗 die 的面积,起到提升良率、降低成本的作用。DAC 2022 会议 上,清华大学冯寅潇发表研究成果,结论表明在 5nm 制程,当芯片面积达到 200mm2 以上,单颗 SOC 的成本将高于 MCM 工艺;当芯片面积达到 400mm2 以上,由于良率的大幅下降,单颗 SOC 方案的成本将高于 InFO 工艺(MCM、 InFO 均为 Chiplet 技术的不同封装形式)。其成本差异就主要在大面积单芯片方 案中的良率损失,在多芯片方案中大幅下降。

(2)HBM 的导入

高性能计算应用对内存速率提出了更高的要求,借助 3D 封装技术的 HBM 则 很好的解决了内存速率瓶颈。 HBM(High Bandwidth Memory)即高带宽存储器,其通过使用先进的封 装方法(如 TSV 硅通孔技术)垂直堆叠多个 DRAM,并在硅 interposer 上与 GPU 封装在一起。HBM 内部的 DRAM 堆叠属于 3D 封装,而 HBM 与 GPU 合 封于 Interposer 上属于 2.5D 封装,是典型的 Chiplet 应用。

(3)允许更多计算核心的“堆料”

由于 chiplet 工艺引入了高速互连的 Interposer 或其他中介层,使得芯片厂 商得以将多颗计算核心 die 进行合封,以提高芯片整体性能。 Apple 的 M1 Ultea 芯片采用了台积电的 InFO_LSI 工艺,将两颗 M1 Max “拼接”,Apple 将其成为 UltraFusion 芯片互连技术。LSI 即本地硅互连(Local Silicon Interconnect),即通过在 RDL 载板中嵌入一块硅桥实现两颗 Die 的高速 互连。

与之类似,2022 年 8 月,国产算力芯片厂商壁仞科技发布 BR100,采用台 积电 CoWoS-S 工艺,将两颗计算核心封在一块硅 Interposer 上,其 16 位浮点 算力达到 1000T 以上、8 位定点算力达到 2000T 以上,创造全球算力纪录。

2.3 行业龙头助力,算力芯片异构化已成大势所趋

得益于 Chiplet 技术在大规模算力芯片领域的优异表现,业内设计公司巨头 纷纷加入推广 Chiplet 成为行业主流方案。2022 年 3 月 3 日,AMD、Intel 等半 导体巨头宣布共同成立 Chiplet 行业联盟,目标共同打造 Chiplet 互连标准、推 进开放生态,并制定了标准规范UCIe,在芯片封装层面确立互联互通的高速接口 标准。

目前市面上的主流算力芯片厂商均导入了 Chiplet 方案,尤其是在 AI 芯片领 域。 Nvdia 方面,当前主力产品 A100/H100 均采用台积电 CoWoS 2.5D 封装, A100 采用 7nm 制程,最高配备 80GB HBM2E;H100 则采用 4nm 制程,并配 备最高 80GB HBM3。 AMD 方面则推出了更大规模的 Chiplet 产品,其 2023 年 6 月 14 日正式发 布的 MI300 AI 加速卡拥有 13 个小芯片,共包括 9 个 5nm 的计算核心(6 个 GCD+3 个 CCD),4 个 6nm 的 I/O die 兼 Infinity Cache(同时起到中介层的作 用,位于计算核心和 interposer 之间),还配备了累计 8 颗共计 128GB 的 HBM3 芯片。相较 Nvdia 的 A/H 系列产品,MI300 更进一步的将 SOC 拆分成了多颗小 芯粒,并拥有更大的面积、芯粒数量、缓存颗粒数量。

国内算力芯片厂商亦在快速跟进,除了前文提到的壁仞科技以外,沐曦、天 数等 AI 芯片厂商亦纷纷推出异构集成的 GPU 产品,导入 HBM 存储,我们相信 Chiplet 的技术优势将使其成为算力芯片未来的主流方案,给产业链各环节带来 价值增量。下文我们将具体讨论 Chiplet 的产业链进展,以及其对国产供应链的 拉动作用。

3 龙头晶圆厂主导 Chiplet 技术路线

3.1 台积电

晶圆代工龙头台积电是 Chiplet 工艺的全球领军者,也是当前业内主流算力 芯片厂商的主要供应商,因此我们将做着重介绍。其于 2021 年将 2.5D/3D 先进 封装相关技术整合推出 3DFabric 平台,由于 Chiplet 技术涉及芯片的堆叠,因此 台积电将其命名为 3DFabric™技术,旗下拥有 CoWoS、InFO、SoIC 三种封装 工艺,代表当前 Chiplet 技术的三种主流形式。Intel 和三星各自都有类似的 2.5D/3D 封装工艺,尽管命名不同,但结构与台积电方案类似。 前段技术 3D SoIC 利用芯片间直接铜键合,具有更小间距;后段技术 2.5D 方面,CoWos 扩展至三种不同转接板技术,InFO 将封装凸块直接连接到再分配 层。

(1)CoWoS

2012 年台积电与 Xilinx 共同开发集成电路封装解决方案 CoWoS,该封装技 术已成为高性能和高功率设计的实际行业标准。CoWoS-S 采用硅中介层,可以 为高性能计算应用提供更高的性能和晶体管密度; CoWoS-R 采用 RDL 中介层, 利用 InFO 技术进行互连,更强调小芯片间的互连; CoWoS-L 融合 CoWoS-S 和InFO 技术优势,使用夹层与 LSI(局部硅互连)芯片进行互连,使用 RDL 层进行 电源和信号传输,提供了灵活的集成。英伟达、博通、谷歌、亚马逊、NEC、 AMD、赛灵思、Habana 等公司已广泛采用 CoWoS 技术。

(2)InFO

2017年台积电宣布2.5D封装技术InFO(Integrated Fanout technology) 集成扇出晶圆级封装。台积电的 InFO 技术使用 polyamide 代替 CoWoS 中的硅 中介层,降低了成本和封装高度,促进大规模生产应用。InFO 具有高密度的 RDL,适用于移动、高性能计算等需要高密度互连和性能的应用。

(3)SoIC

2019 年台积电推出 SoIC 技术,包括 chip-on-wafer(COW)和 wafer-on-wafer(WOW)两种方案。与 CoWoS 和 InFO 不同,前面两种方案是在封 装环节将完成晶圆级封装的逻辑芯片、HBM、Interposer等进行堆叠,因此成为 后道 3D 制造(Back End 3D Fabric),而 SoIC 是在前道晶圆制造环节,就在逻 辑芯片上制造 TSV 通孔,并将逻辑芯片之间(或逻辑芯片的晶圆之间)进行堆叠, 这个过程称为前道 3D 制造(Front End 3D Fabric),完成堆叠后的晶圆切割后 可再进行类似 InFO 和 CoWoS 的后道封装。因此,SoIC 与 InFO/CoWoS 并非 并列、替代关系,而是将 InFO/CoWoS 所用到的单颗 SoC 替换成了经过 3D 堆 叠的多颗 SoC。 SoIC 是台积电异构小芯片封装的关键,具有高密度垂直堆叠性能,与 CoWoS 和 InFO 技术相比 SoIC 可以提供更高的封装密度和更小的键合间隔。

3.2 Intel

作为全球 CPU 设计龙头厂商,Intel 同时亦是领先的 IDM 厂商。其主推的 Chiplet 工艺包括 EMIB 和 Foveros,分别类似于台积电的 InFO_LSI 和 SoIC。 EMIB 是 2.5D 硅中介层的替代方案,die-substrate 互连通过传统覆晶芯片 方式,die-die 桥接的部分用一个很小的 Si 片实现,并将这部分嵌入在载板内, 和硅中介层(interposer)相比,EMIB 硅片面积更微小、更灵活、更经济;与 传统 2.5D 封装的相比,因为没有 TSV,因此 EMIB 技术具有正常的封装良率、无 需额外工艺和设计简单等优点。

Foveros技术是高于EMIB技术的3D芯片堆叠技术,利用晶圆级封装能力, 与 2D 的 EMIB 封装方式相比,Foveros 更适用于小尺寸产品或对内存带宽要求 更高的产品。与 TSMC 的 SoIC/CoWoS/InFO 的关系类似,Foveros 与 EMIB 亦 可以配合使用。

3.3 三星

三星基于“超越摩尔定律”方法的异构集成技术,沿着水平集成和垂直集成 两种方向,先后研发出三大先进封装技术:I-Cube、H-Cube 和 X-Cube。 I-Cube 和 H-Cube 是 2.5D 封装方案。I-CUBE-S 类似台积电的 CoWoS-s, I-CUBE-E 类似台积电的 CoWoS-L。H-Cube 方案则抛弃了大面积的 ABF 基板, 采用面积较小的 ABF 基板或 FBGA 基板叠加大面积的 HDI 基板的方式。 X-Cube 则采用在 3D 空间堆叠逻辑裸片的方法,类似台积电的 SoIC 方案。 而在芯片之间的互连方式上,X-Cube 可以采用传统的 u-bump,也可以使用更 高端的混合键合(Hybrid Bonding),Hybrid Bonding 可以容纳更高的 I/O 密 度。

4 Chiplet 技术带来国产供应链机遇

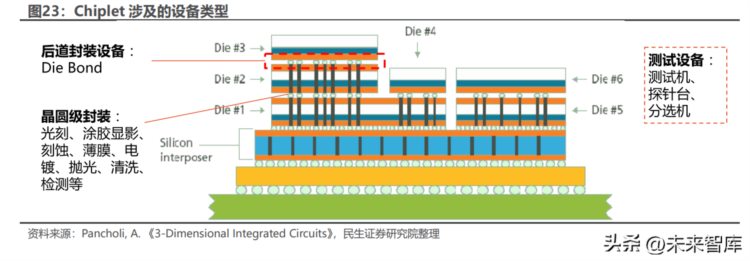

本章我们将重点讨论 Chiplet 技术应用,尤其是增长潜力较大的算力芯片 2.5D/3D 封装带来的国产供应链机遇。主要包括: 1)封测端:算力芯片广泛采用的 2.5D/3D 封装方案是对传统封装的重大升 级,但封测厂商仍将扮演重要地位。尤其是在晶圆级封装等领域,与过去的 FC 封装有共通之处。 2)设备端:Chiplet 技术带来芯片数量的增长,测试设备用量。此外 Chiplet 技术还增加了晶圆级封装的需求,诸多晶圆制造设备迎来需求增量。 3)材料端:Chiplet 技术对芯片的高速互联需求增长,带来高速封装基板需 求,此外高端封装耗材的用量亦会有所增加。

4.1 封装:晶圆厂主导,封装厂商配套导入中

算力芯片的 2.5D/3D 封装主要包括中段晶圆级封装+后段封装。以台积电 CoWoS 封装为例: 1)晶圆级封装:计算核心等芯片晶圆制造完成后在重构晶圆上制造 RDL 和 bump; 2)COW:将计算核心、I/O die、HBM 等芯片封装在 Interposer 上,即为 CoWoS(chip on wafer on substrate)的 chip on wafer 环节; 3)OS:完成 CoW 封装的整个系统在封装基板上封装,这一步即 CoWoS 的 on substrate 环节,其封装方式与传统的 FCBGA 的后段封装基本类似。

与传统的产业链分工不同的是,2.5D/3D 封装是在晶圆制造和传统的后段封 装之间增加了额外的环节,因此晶圆厂和封装厂均有参与机会。当前台积电基本 垄断了全球算力芯片的 2.5D 封装市场,受益于算力芯片需求攀升,正在积极扩充封装产能。 而于此同时,国内龙头封装厂亦在积极把握行业机遇,导入客户 Chiplet 产 品供应链。通富微电已经具备 7nm Chiplet 规模量产能力,并持续与 AMD 等龙 头厂商加深合作;长电科技推出 XDFOI™技术方案,已经实现国际客户 4nm 节点 Chiplet 产品的量产出货。 此外,Chiplet 应用加速了晶圆级封装的需求,国内诸多封测厂商都具备晶 圆级封装能力,诸如长电科技、通富微电、华天科技、甬矽电子、盛合晶微等, 有望迎来晶圆级封装的需求增量。我们看好 Chiplet 技术应用提速之下国内先进 封装厂商的发展机遇。

4.2 设备:晶圆级封装设备和后道封测设备需求增长

Chiplet 应用对设备的需求拉动来自两方面: 1)晶圆级封装设备。晶圆级封装需要的设备与前道晶圆制造类似,涉及光 刻机、涂胶显影设备、薄膜设备、电镀设备、刻蚀设备、清洗设备、量测设备等。 国产诸多公司都有相关业务:北方华创(刻蚀、薄膜、清洗等)、芯源微(涂胶 显影、清洗)、盛美上海(电镀、清洗、涂胶显影、抛光)、中科飞测(检测)等。 2)后道封测设备。Chiplet 封装依旧需要和传统封装类似的封装和测试环节, 有望成为国产封测设备厂商成长的新动力,包括:封装设备厂商新益昌、ASMP; 测试设备厂商长川科技、华峰测控、金海通等。

4.3 材料:ABF 载板用量提升

Chiplet 技术发展增大芯片封装面积,提升 ABF 载板用量。Chiplet 是将一 类满足特定功能的 die(裸片),通过 die-to-die 内部互联技术实现多个模块芯片与底层基础芯片封装在一起,形成一个系统芯片,要将这些芯片整合在一起需要 更大的 ABF 载板来放置,这意味着 ABF 载板耗用的面积将随 chiplet 技术而变 大,而载板的面积越大,ABF 的良率就会越低,ABF 载板需求也会进一步提高。 同时,Chiplet 先进封装的应用也会增加封装载板层数,具体层数与技术指标 要求取决于芯片的设计方案。

ABF 载板已经成为 FC-BGA 封装的标配。ABF 载板又被称为味之素基板, 其关键材料 ABF 膜被日本味之素公司垄断,是 FC-BGA 封装的标配材料。ABF 载 板作为芯片封装中连接芯片与电路板的中间材料,主要用于 CPU、GPU、FPGA、 ASIC 等高运算性能芯片,其核心作用就是与芯片进行更高密度的高速互联通信, 然后通过载板上的更多线路与大型 PCB 板进行互联,起着承上启下的作用,进而 保护电路完整、减少漏失、固定线路位置、有利于芯片更好的散热以保护芯片, 甚至可埋入无源、有源器件以实现一定系统功能。 ABF 载板厂商主要集中在中国台湾、日本和韩国。根据 QYResearch 统计及 预测,2021 年全球 ABF 基板市场销售额达到 43.68 亿美元,预计 2028 年将达 到 65.29 亿美元,CAGR 为 5.56%。目前 ABF 载板主要有七大供货商,2021 年 供货比重分别是欣兴 21.6%、Ibiden 19.0%、AT&S 16.0%、南电 13.5%、 Shinko 12.1%、景硕 7.2%、Semco 5.1%,2022 年除 Semco 外,其余厂商于 皆有进行扩产。从生产端来看,日本、中国台湾和韩国主导了全球 ABF 载板生产, 2021 年这三大地区的市场份额分别为 25%、44%和 9.9%。

未来随着 CPU、GPU、FPGA、ASIC 等高性能运算芯片需求增长以及 Chiplet 技术的广泛应用,ABF 载板的需求量将进一步提升。国内厂商如华正新 材、生益科技、方邦股份、兴森科技、深南电路等正在加快核心技术研发,力争 打破海外垄断格局。目前华正新材的 CBF 积层绝缘膜正在加快新产品开发进程, 在 CPU、GPU 等半导体芯片封装领域进入了下游 IC 载板厂、封装测试厂及芯片 终端验证流程,并取得了良好进展。

5 投资分析

长电科技

长电科技成立于 1972 年,是全球领先的集成电路制造和技术服务企业。主 营业务包括集成电路的系统集成、设计仿真、技术开发、产品认证、晶圆中测、 晶圆级中道封装测试、系统级封装测试、芯片成品测试。公司全面覆盖主流中高 低封测技术,并覆盖 WLP、2.5D/3D、SIP、高性能倒装芯片、引线互联等先进 技术;业务实现对汽车领域、通信领域、高性能计算领域、存储领域的覆盖。长 电旗下生产基地全球布局,拥有主营先进封装的星科金朋、长电韩国、长电先进、 长电江阴,和主营传统封装的滁州、宿迁多个厂区。

长电科技在中国、韩国和新加坡拥有两大研发中心和六大集成电路成品生产 基地,星科金朋、长电先进、长电韩国主营先进封装业务,而长电本部江阴厂、 宿迁厂和滁州厂主营传统封装业务。各生产基地分工明确、各具技术特色和竞争 优势。 2022 年半导体封测行业景气下行,但公司加快高性能封测领域的研发和客 户产品导入,强化高附加值市场的开拓,优化产品结构和业务比重,实现收入和 净利润逆势增长。2022 年全年,公司实现营收 337.62 亿元,同比增长 10.69%; 实现归母净利润 32.31 亿元,同比增长 9.20%,创历年新高。 2023 年 Q1,受半导体周期性下行影响,公司业绩短期承压,实现归母净利 润 1.10 亿元,同比下滑 87.24%,实现营收 58.60 亿元,同比下滑 27.99%。

利润率和费用率方面,公司在过去数年间通过业务规模增长、运营管理精进, 实现了较好的降费增效和盈利释放。2017-2022 年,公司毛利率从 11.71%提升 至 17.04%,期间费用率从 13.55%下降至 7.47%,2019 年实现扭亏为盈,2022 年实现净利率 9.57%。2023 年 Q1,受行业景气度影响公司毛利率短期下滑至 11.84%,净利率同步下滑至 1.88%。

从下游市场结构来看,公司下游市场以通信和消费电子为主。2022 年全年, 公司收入结构中通讯电子占比 39.3%、消费电子占比 29.3%、运算电子占比 17.4%、工业及医疗电子占比